模擬CMOS集成電路設(shè)計習(xí)題解析與學(xué)習(xí)建議

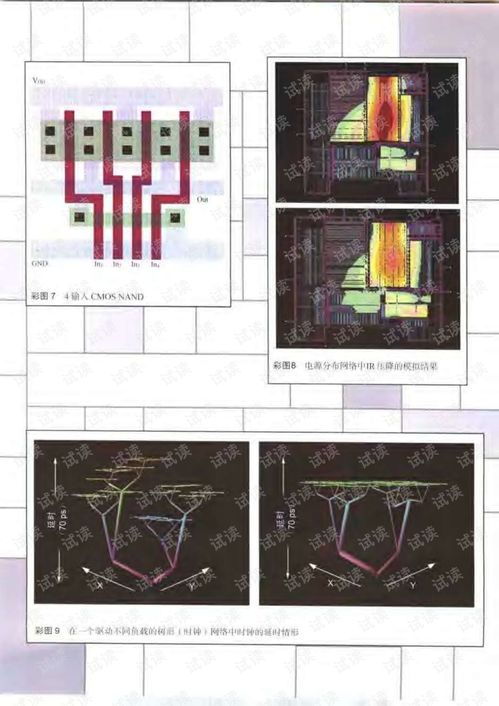

模擬CMOS集成電路設(shè)計是電子工程領(lǐng)域的核心課程,涉及放大器、偏置電路、頻率響應(yīng)等多個關(guān)鍵模塊。以下針對常見習(xí)題類型提供解題思路和學(xué)習(xí)建議:

一、單級放大器設(shè)計類習(xí)題

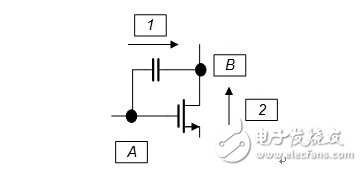

典型問題:計算共源極放大器的電壓增益、輸出阻抗和帶寬

解題要點:

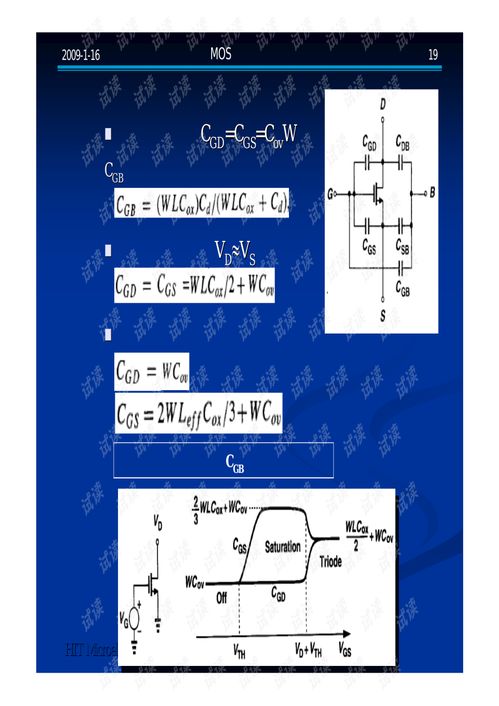

1. 明確工作區(qū)(飽和區(qū)/線性區(qū))

2. 使用小信號模型推導(dǎo)傳遞函數(shù)

3. 注意負(fù)載電容對頻率響應(yīng)的影響

示例:通過gm·ro公式計算增益,利用密勒效應(yīng)分析高頻極點

二、偏置電路設(shè)計題

重點考察電流鏡、電壓基準(zhǔn)等結(jié)構(gòu)

解題步驟:

1. 分析晶體管匹配關(guān)系

2. 建立KCL/KVL方程

3. 考慮工藝偏差的影響

提示:使用λ參數(shù)計算輸出阻抗,注意溝道長度調(diào)制效應(yīng)

三、頻率響應(yīng)分析題

常見要求:繪制波特圖,計算主極點位置

方法論:

1. 識別電路中的電容節(jié)點

2. 應(yīng)用開路時間常數(shù)法

3. 區(qū)分低頻/高頻響應(yīng)特性

技巧:先計算每個獨立電容的時間常數(shù),再求總和得帶寬

四、噪聲性能計算題

解題關(guān)鍵:

1. 區(qū)分熱噪聲與閃爍噪聲

2. 計算等效輸入噪聲

3. 優(yōu)化器件尺寸降低噪聲

提醒:注意噪聲系數(shù)與功耗的折衷關(guān)系

學(xué)習(xí)建議:

- 掌握MOSFET的I-V特性方程

- 熟練使用小信號模型分析方法

- 建立直觀的電路物理圖像

- 通過仿真軟件驗證計算結(jié)果

- 關(guān)注現(xiàn)代工藝下的設(shè)計約束

建議參考《模擬CMOS集成電路設(shè)計》(拉扎維著)的例題,結(jié)合Cadence等工具進(jìn)行實踐,逐步培養(yǎng)解決復(fù)雜設(shè)計問題的能力。

如若轉(zhuǎn)載,請注明出處:http://m.ruling123.cn/product/9.html

更新時間:2026-04-14 19:44:27